PCIe, SAS, SATA 컴플라이언스 테스트 가속화

페이지 정보

본문

차세대 데이터 속도 경쟁에 지금 대비

클라우드 컴퓨팅, IOT, 인공 지능과 같은 차세대 혁신 기술은 이에 따른 문제점도 내포하고 있습니다. PCIe와 같은 스토리지 표준이 4세대에서 5세대로 전환하면서 데이터 속도 증가,

채널 손실 및 ISI(기호 간 간섭) 극복, 획득 및 분석의 완전 자동화, 물리적 및 프로토콜 계층에서의 디버깅을 보다 면밀히 주시하게 될 것입니다.

이처럼 차세대 데이터 속도 및 스토리지 표준을 충족하기 위해서는 현재 세대의 기능을 제공하면서 32Gb/s까지 확장할 수 있는 엔드 투 엔드 솔루션(end-to-end)이 필요합니다.

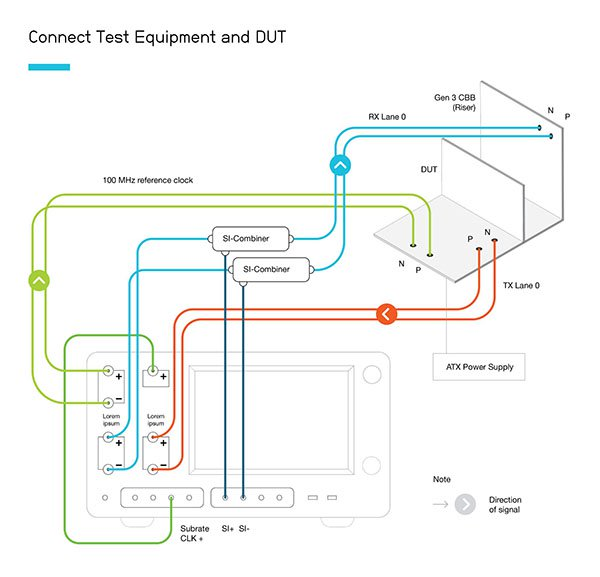

교정 자동화(Automated Calibration) 16Gb/s 이상의 수동 교정은 시간이 상당히 많이 소요되는 작업으로 작업자를 지치게 하기 쉽습니다. 자동 단계별 교정 위저드는 테스트 설정이 올바른지 확인하여 귀중한 시간과 비용을 절감하도록 하는 데 반드시 필요한 기능입니다. 데이터 획득, 컴플라이언스 분석 및 이퀄라이제이션 과정을 모두 자동화하여 설계 주기 및 시장 출시시간을 단축할 수 있습니다. 텍트로닉스는 자동화 및 디버그 기능을 비롯한 PCIe, SAS 및 SATA용 스토리지 및 서버 표준에 맞는 가장 완전한 단독 벤더 테스트 솔루션(32Gb/s 속도)을 제공합니다. Gen4 I/O 애플리케이션의 리시버 테스트 문제 해결 방법 자세히 보기 | 자동 교정 설정으로 귀중한 시간을 절약하세요. |

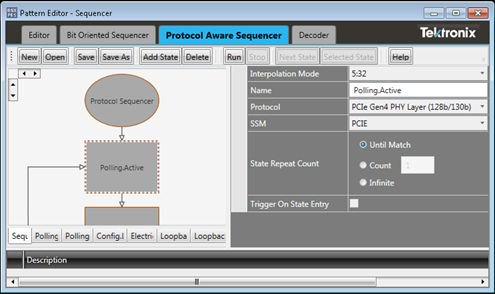

루프백 디버그에서 루프 닫기 이미 경험해 보신 분도 있겠지만, 시스템 및 AIC 설계 복잡성이 증가하면서 Gen4 DUT의 루프백 시작 및 핸드셰이킹을 디버그하는 데 몇 시간이 걸릴 수도 있습니다. 또한, 테스트 실패 시 잘못된 부분을 명확히 파악하지 못할 수도 있습니다. 즉, 복잡한 프로토콜 핸드셰이크 문제를 보다 빠르게 파악할수록 더 나은 결과를 얻을 수 있습니다. 텍트로닉스의 BSX 시리즈 BERTScope는 문제발생 시 근본 원인을 찾는 데 필요한 정보를 제공할 수 있도록 사용자 정의 가능한 패턴 시퀀서 기능 및 캡처 후 디코딩 트리거 기능을 제공합니다. | 프로토콜 인식 시퀀서를 사용하여 DUT를 간편하고 효율적으로 루프백 모드로 전환하거나 링크 연결 프로세스를 완료할 수 있습니다. |

뛰어난 신호 무결성 및 디버그

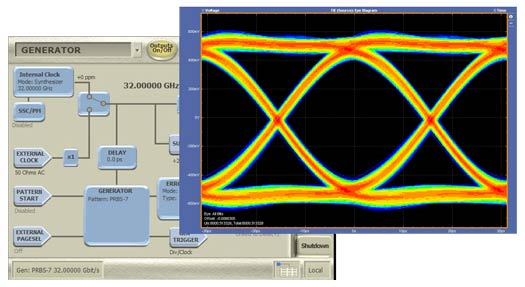

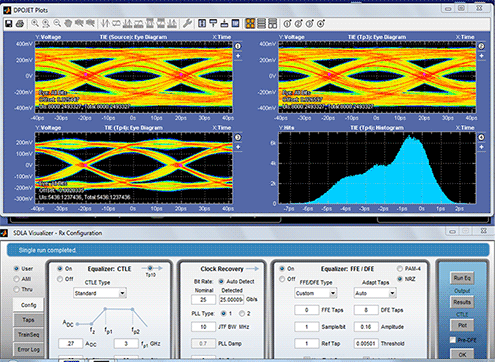

늘어나면서 손실 채널 끝을 명확히 파악하는 데 동급 최고의 신호 무결성 테스트 및 디버그 도구가 반드시 필요합니다. 텍트로닉스는 트랜스미터 및 리시버 테스트를 위해 이러한 도구를 제공합니다. 텍트로닉스는 뛰어난 안정성과 더불어 최저 노이즈 소음의 DPO70000SX 스코프와 BSX 시리즈 BERTScope 비트 에러 찾기 도구를 사용하여 병리적 비트 에러 문제의 근본 원인을 파악하는 이퀄라이제이션 및 S-파라미터손실 디임베딩을 위한 뛰어난 정밀도 측정 SDLA 도구를 제공합니다. 비트 에러의 정확한 비트 위치 및 타이밍 확인을 위한 간단한 전략에 대해 자세히 보기 | |

주요 콘텐츠 |

|

|

PCI Express에 대해 알아두어야 할 10가지 사항 | 보다 빠르게 PCIe 컴플라이언스 이해하기 | Gen4 I/O 애플리케이션에서 수신기 테스트 문제 해결 |

레퍼런스 가이드 | 웹 세미나 | 애플리케이션 노트 |

유의해야 할 송신기 및 수신기 테스트 절차와 함께, PCIe Gen4의 새로운 기능 개요, 루프백 시작 및 프로토콜 핸드셰이킹을 비롯하여 포괄적인 디버그 프로세스 설정 시 필요한 핵심 고려 사항을 통해 계속해서 변화하는 표준의 중요한 측면을 이해할 수 있습니다. | 이 웹 세미나는 PCIe 장치의 테스트 프로세스에 대한 정보를 제공하여 컴플라이언스를 보다 빠르게 이해할 수 있도록 합니다. | 이 새로운 애플리케이션 노트를 다운로드하여 비트 에러율 테스터로 Gen4 엔터프라이즈 수신기에 대해 컴플라이언스 및 진단 테스트를 수행하는 데 필요한 핵심 정보를 확인하십시오. |

| ||

신호의 진정한 특성을 정확한 측정값으로 표현 | 물리 계층 및 링크 연결의 디버그 시간 단축 | PCI Express 솔루션 |

| 32Gb/s의 프로토콜 링크 연결을 관찰해서 디버그하고, 루프백 시작 및 링크 연결에 대한 컴플라이언스 테스트 및 사용자 정의 가능한 패턴 시퀀서를 자동화합니다. |

|

업계 최저 노이즈를 자랑하는 DPO70000SX 실시간 오실로스코프는 가장 정확한 특성화 및 마진 분석을 수행할 수 있습니다. | 현재 및 차세대 PCIe 사양(표준 1, 2, 3세대 및 현재의 PCIe 4.0)에 대한 심도 깊은 분석, 자동화된 컴플라이언스 테스트 및 디버그를 수행할 수 있습니다. | |

| | |

SAS/SATA 솔루션 |

|

|

|

| |

|

|

|

현재와 차세대 SAS 및 SATA 인터페이스에 대해 단독 벤더로 제공하는 자동화된 Tx 및 Rx 컴플라이언스 도구로 테스트 설정을 간소화하고 심층적인 오류 분석을 수행할 수 있습니다. |

|

|

|

|

댓글목록

등록된 댓글이 없습니다.